## SG 280 FPGA Module

00101000101110001010000100011100

00001111100101000101110001010000101

10101000010111000001110100110100010

## **Product Summary**

The proFPGA SG 280 FPGA module is the logic core for the scalable and modular multi-FPGA proFPGA solution, which fulfills highest needs in the area of FPGA based Prototyping. It addresses customers who need a scalable and most flexible high performance ASIC Prototyping solution for early software development and real-time system verification. The innovative system concept and technologies offer highest flexibility and reusability for several projects, which guarantees the best return on invest.

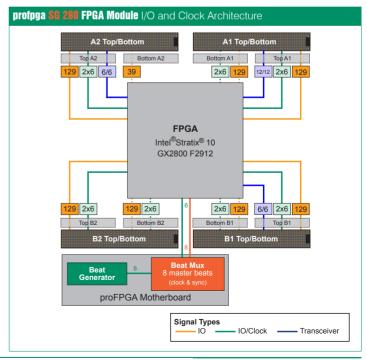

The proFPGA SG 280 FPGA module, which only works in combination with a proFPGA uno, duo or quad motherboard, offers with its latest Intel® Stratix® 10 FPGA technology a maximum capacity of up to 20 M ASIC gates alone in one FPGA. It is designed to achieve highest performance in combination with its high speed connectors. The module offers with its 8 extension sites up to 1026 user I/Os for daughter boards (e.g. memory or interface boards), interconnect cables or customer specific application boards.

In addition to the regular I/Os the module also provides 24 high speed serial transceivers ( $1 \times 12$  and  $2 \times 6$  Transceiver Tiles) running up to 17.4 Gbps for high speed interfaces like PCle Gen4. All of the 8 extension sites offer individually and stepless adjustable voltage regions from 1.2V up to 1.8V.

| profpga SB 280 FPGA Module Specification |                                                                                                                                                         |

|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| FPGA Type                                | - Intel <sup>®</sup> Stratix <sup>®</sup> 10 GX2800 F2912 (speedgrade 1/2/3)                                                                            |

| Capacity                                 | - Up to 20 M ASIC gates                                                                                                                                 |

| FPGA memory                              | - 229 Mbit                                                                                                                                              |

| DSP blocks                               | - 5760                                                                                                                                                  |

| Signaling rate                           | - Standard I/Os: up to 1 Gbps single ended<br>- Transceiver Tiles: up to 17.4 Gbps                                                                      |

| Extension sites                          | - 8 extension sites with high performance connectors                                                                                                    |

| I/O resources                            | - Overall 1026 signals  - 4 x 141 I/Os to top side connectors  - 3 x 141 I/Os and 1 x 39 I/Os to bottom side connectors  - Single-ended or differential |

| High speed I/O transceivers              | - Overall 24 high speed transceivers on top side<br>- 1 x 12 and 2 x 6 transcievers to top side connectors                                              |

| Voltage regions                          | - 8 individually adjustable voltage regions per FPGA Module<br>- Stepless from 1.2 up 1.8V<br>- Automated voltage adjustment for daughter boards        |

| Configuration                            | - Via Ethernet, USB on PCle                                                                                                                             |

| Order Code                               | - PROF-FM-ASG280-1/-2/-3 (speedgrade 1/2/3)                                                                                                             |